# Scenario-Based Meta-Scheduling for Energy-Efficient, Robust and Adaptive Time-Triggered Multi-Core Architectures

# **DISSERTATION**

zur Erlangung des Grades eines Doktors der Ingenieurwissenschaften (Dr.-Ing.)

vorgelegt von

M.Sc. Babak Sorkhpour

eingereicht bei der Naturwissenschaftlich-Technischen Fakultät der Universität Siegen

Siegen – July 2019

Gedruckt auf alterungsbeständigem holz- und säurefreiem Papier.

### Betreuer und erster Gutachter

Prof. Dr. Roman Obermaisser, Universität Siegen

**Zweiter Gutachter**

Prof. Dr. Raimund Kirner, University of Hertfordshire

# Prüfungskommission:

Prof. Dr. Roman Obermaisser

Prof. Dr. Raimund Kirner

Prof. Dr. Kristof Van Laerhoven

Prof. Dr. Madjid Fathi (Vorsitz der Prüfungskommission)

Tag der mündlichen Prüfung: 09. July 2019

# Scenario-Based Meta-Scheduling for Energy-Efficient, Robust and Adaptive Time-Triggered Multi-Core Architectures

#### **DISSERTATION**

to obtain the degree of Doctor of Science Engineering

Submitted by M.Sc. Babak Sorkhpour

Submitted to the Faculty of Natural Sciences and Technology

the University of Siegen

Siegen July 09, 2019

I dedicate this dissertation to my parents, my son, and my family.

# Acknowledgements

First, I would like to express my special appreciation, regards, gratitude, and thanks to my advisor Professor Dr. Roman Obermaisser for his assistance and guidance. You have been a tremendous mentor and life coach for me, showing admirable patience.

I would also like to thank Professor Dr. Madjid Fathi and Professor Dr. Raimund Kirner for their encouragement and advice, allowing me to overcome challenges and grow as a research scientist.

I offer special thanks to my family, including my parents, my sister, and my brother, for their endless and immeasurable love and support, especially throughout this part of my life.

I give special thanks to my wonderful son for his unconditional love, support, and understanding. This heroic man is my constant motivation and source of hope.

Finally, and above all, I am profoundly and forever indebted to the creator of love, my Lord, for his unconditional love, support, and encouragement throughout my life.

It is my pleasure and honor to express my gratitude to all the people who contributed, in whatever manner, to the success of this work.

Babak Sorkhpour Siegen July 10, 2019

# Declaration of authorship

I hereby certify that this dissertation and its context has been written by me and is based on my own research work, unless mentioned otherwise. No other person's work, research, or publication has been used in this thesis without due acknowledgement. All references and verbatim extracts have been quoted, and all sources of data and information, including graphs, figures, tables, and data sets, have been specifically acknowledged.

#### ABSTRACT

Complex electronic systems are used in many safety-critical applications (e.g., aerospace, automotive, nuclear stations), for which certification standards demand the use of assured design methods and tools. Scenario-based meta-scheduling (SBMeS) is a way of managing the complexity of adaptive systems via predictable behavioral patterns established by static scheduling algorithms. SBMeS is highly relevant to the internet of things (IoT) and real-time systems. Real-time systems are often based on time-triggered operating systems and networks and can benefit from SBMeS for improved energy-efficiency, flexibility and dependability.

This thesis introduces an SBMeS algorithm that computes an individual schedule for each relevant combination of events such as dynamic slack occurrences. Dynamic frequency scaling of cores and routers is used to improve energy efficiency while preserving the temporal correctness of time-triggered computation and communication activities (e.g., collision avoidance, timeliness). Models of applications, platforms and context are used by scheduling tools to prepare reactions to events and to generate meta-schedules.

In this work, techniques and tools are developed to schedule a set of tasks and messages on Network-on-chip (NoC) architectures to minimize total energy consumption, considering time constraints and adjustable frequencies. This algorithm is intended for mixed-criticality and safety-critical adaptive time-triggered systems and can cover fault-tolerance requirements. It can also help to react to fault events by recovering the system. We also introduce a meta-scheduling visualization tool (MeSViz) for visualizing schedules. We also introduce a meta-scheduling visualization tool (MeSViz) for visualizing schedules.

We experimentally and analytically evaluate the schedules' energy-efficiency for cores and routers. In addition, the timing is analytically evaluated, based on static slack and dynamic slack events. Simulation results show that our dynamic slack algorithm produces, on average, an energy reduction of 64.4% in a single schedule and 41.61% energy reduction for NoCs. By compressing the schedule graphs the memory consumption can be reduced by more than 61%.

#### KURZBESCHREIBUNG

In vielen sicherheitskritischen Anwendungen (z.B. Luft- und Raumfahrt, Automotive, Kernkraftwerke) kommen komplexe elektronische Systeme zum Einsatz, für die Zertifizierungsnormen den Einsatz von sicheren Konstruktionsmethoden und -tools vorschreiben. Die Szenario-basierte Meta-Planung (SBMeS) ist eine Möglichkeit, die Komplexität von adaptiven Systemen über vorhersehbare Verhaltensmuster zu steuern, die durch statische Planungsalgorithmen festgelegt werden. SBMeS ist sehr bedeutsam für das Internet der Dinge (IoT) und Echtzeitsysteme. Echtzeitsysteme basieren oft auf zeitgesteuerten Betriebssystemen und Netzwerken und können von SBMeS für mehr Energieeffizienz, Flexibilität und Zuverlässigkeit profitieren.

Diese Abhandlung stellt einen SBMeS-Algorithmus vor, der einen individuellen Zeitplan für jede relevante Kombination von Ereignissen wie dynamische Schlupfereignisse berechnet. Die dynamische Frequenzskalierung von Prozessorkernen und Routern dient der Verbesserung der Energieeffizienz unter Beibehaltung der zeitlichen Korrektheit von zeitgesteuerten Berechnungs- und Kommunikationsaktivitäten (z.B. Kollisionsvermeidung, Echtzeitfähigkeit). Mit Hilfe von Modellen von Anwendungen, Plattformen und Kontexten werden Planungswerkzeuge eingesetzt, um Reaktionen auf Ereignisse vorzubereiten und Meta-Planungen zu generieren.

Im Rahmen dieser Arbeit werden Techniken und Werkzeuge entwickelt, um eine Reihe von Berechnungen und Nachrichten auf Network-On-Chip (NoC)-Architekturen zu planen, mit dem Ziel, den Gesamtenergieverbrauch unter Berücksichtigung von Zeitvorgaben und einstellbaren Frequenzen zu minimieren. Der Algorithmus unterstützt sicherheitskritische adaptive zeitgesteuerte Systeme und kann die Anforderungen hinsichtlich der Fehlertoleranz abdecken. Er kann auch dazu beitragen auf Störungsfälle zu reagieren, indem er das System wiederherstellt. Außerdem stellen wir ein Meta-Planungstool (MeSViz) zur Visualisierung von zeitgesteuerten Plänen vor.

Wir analysieren und bewerten die Energieeffizienz der Pläne experimentell für Prozessorkerne und Router. Darüber hinaus wird das Zeitverhalten anhand von statischen und dynamischen Schlupfereignissen analytisch bewertet. Simulationsergebnisse zeigen, dass unser dynamischer Schlupfalgorithmus im Durchschnitt eine Energieeinsparung von 64,4% in einem einzigen Zeitplan und 41,61% Energieeinsparung für NoCs erbringt. Durch die Komprimierung der Zeitpläne kann der Speicherverbrauch um mehr als 61% reduziert werden.

# List of Abbreviations

| WCET       | Worst-case execution time             |  |

|------------|---------------------------------------|--|

| TTEthernet | Time-triggered ethernet               |  |

| NoC        | Network-on-a-chip                     |  |

| CAN        | Controller area network               |  |

| MPSoC      | Multi-processor-system-on-a-chip      |  |

| MILP       | Mixed integer linear programming      |  |

| MPSoC      | Multi-processor system-on-a-chip      |  |

| MeS        | Meta-scheduler                        |  |

| SBMeS      | Scenario-based meta-scheduling        |  |

| MeSViz     | Meta-schedule visualizer              |  |

| TT         | Time-triggered                        |  |

| TTS        | Time-triggered systems                |  |

| TTN        | Time-triggered network                |  |

| TTC        | Time-triggered communication          |  |

| TTA        | Time-triggered architecture           |  |

| LIN        | Local interconnect network            |  |

| DVFS       | Dynamic voltage and frequency scaling |  |

| SDF        | Slow-down factor                      |  |

| TSDF       | Task slow-down factor                 |  |

| MSDF       | Message slow-down factor              |  |

# Contents

| ABSTR   | ACT                                                                                           | 7           |

|---------|-----------------------------------------------------------------------------------------------|-------------|

| KURZB   | ESCHREIBUNG                                                                                   | 8           |

| CONTE   | NTS                                                                                           | 10          |

| СНАРТ   | ER 1: INTRODUCTION                                                                            | 15          |

| 1.1.    | MOTIVATION                                                                                    | 16          |

| 1.2.    | Research scope                                                                                | 19          |

| 1.3.    | STRUCTURE OF THE THESIS                                                                       | 20          |

| СНАРТ   | ER 2: RELATED WORK AND BASIC CONCEPTS                                                         | 22          |

| 2.1. R  | LEAL-TIME SYSTEMS                                                                             | 22          |

| 2.1     | 1.1. Embedded real-time systems                                                               | 22          |

|         | 2.1.1.1. Makespan                                                                             |             |

|         | 1.2. Dependability                                                                            |             |

|         | 2.1.2.1. Mixed-criticality systems                                                            | 23          |

| 2.1     | 1.3. Adaptivity                                                                               | 24          |

| 2.2. T  | IME-TRIGGERED SYSTEMS (TTSs)                                                                  | 24          |

| 2.3. G  | GLOBAL TIME BASE                                                                              | 24          |

|         | 3.1. Time-triggered networks (TTNs)                                                           |             |

|         | 2.3.1.1. Messages                                                                             |             |

| 2.3     | 3.2. Time-triggered multi-processor system-on-a-chip (MPSoC) and network-on-a-ci              | hip (NoC)25 |

| 2.3     | 3.3. Time-triggered (TT) execution environments                                               | 27          |

|         | 2.3.3.1. Tasks                                                                                |             |

|         | 2.3.3.2. Worst-case execution time (WCET)                                                     | 27          |

|         | 2.3.3.3. Slack                                                                                | 28          |

| 2.4. E  | NERGY MANAGEMENT TECHNIQUES                                                                   | 28          |

| 2.4     | 4.1. Clock gating and power gating                                                            | 28          |

|         | 2.4.1.1. Dynamic voltage and frequency scaling (DVFS)                                         | 28          |

|         | 2.4.1.1.1. Frequency tuning on network-on-chip (NoC)                                          |             |

|         | 2.4.1.1.2. Distributed dynamic voltage and frequency scaling (DVFS) algorithm at the roulevel |             |

|         | 2.4.1.1.3. Worst case execution times (WCETs) and distributed dynamic voltage and frequ       |             |

|         | (DVFS)                                                                                        |             |

| 2.5. E  | NERGY MANAGEMENT FOR DIFFERENT TYPES OF RESOURCES                                             |             |

|         | 5.1. Network-on-chip (NoC)                                                                    |             |

|         | 5.2. Processor                                                                                |             |

|         | 5.3. Task procrastination and slack reclamation                                               |             |

|         | CHEDULING FOR TIME-TRIGGERED SYSTEMS (TTS)                                                    |             |

|         | 5.1. Algorithms for static                                                                    |             |

|         | 2.6.1.1. Static scheduling for energy efficiency                                              |             |

|         | 2.6.1.2. Static scheduling for reliability                                                    |             |

|         | 5.2. Meta-scheduling (MeS) and mode changes                                                   |             |

|         | 5.3. Optimization techniques for scheduling                                                   |             |

|         | 2.6.3.1. Quadratic Optimization                                                               |             |

|         | 2.6.3.2. Mixed integer quadratic programming (MIQP)                                           |             |

|         | 2.6.3.3. Genetic algorithm (GA) and optimization techniques                                   | 35          |

| 2.7. So | CENARIO-BASED SCHEDULING IN EVENT-TRIGGERED SYSTEMS                                           | 36          |

| 2.7.1. Reliability and redundancy in scenario-based meta-scheduling (SBMeS) | 37 |

|-----------------------------------------------------------------------------|----|

| 2.7.2. Scenario-based meta-scheduling (SBMeS) for reconfigurable systems    | 37 |

| 2.7.3. Scenario-based meta-scheduling (SBMeS) for robust systems            | 38 |

| 2.8. OVERVIEW OF SCHEDULING-RELATED WORKS                                   | 38 |

| 2.9. Summary                                                                | 39 |

| 2.10. VISUALIZATION OF SCHEDULES                                            | 40 |

| CHAPTER 3: SYSTEM MODEL                                                     | 42 |

| 3.1. OVERVIEW OF THE MODELS                                                 | 42 |

| 3.2. Input models for a meta-scheduler (MeS)                                | 42 |

| 3.2.1. The physical model (PM)                                              |    |

| 3.2.2. The application model (AM)                                           | 43 |

| 3.2.3. The context model (CM)                                               |    |

| 3.2.4. The schedule model (SM)                                              |    |

| 3.3. MODELLING OF THE OPTIMIZATION PROBLEM                                  |    |

| 3.4. CHOICE OF OPTIMIZATION TECHNIQUE                                       | 46 |

| 3.5. STATIC SCENARIO-BASED META-SCHEDULING (SBMES) AND MAPPING POLICY       |    |

| 3.6. DECISION VARIABLES, CONSTANTS, AND CONSTRAINTS                         |    |

| 3.7. Definitions                                                            |    |

| 3.7.1. Collision avoidance constraint                                       |    |

| 3.7.2. Connectivity constraints                                             |    |

| 3.7.2.1. Links reliability                                                  |    |

| 3.7.3. Task allocation and assignment constraints                           |    |

| 3.7.4. Message duration                                                     |    |

| 3.7.5. Path and visited cores                                               |    |

| .3.7.6 Task dependency constraints                                          | 51 |

| 3.7.7. Message deadlines                                                    |    |

| 3.8. Decision variables                                                     |    |

| 3.8.1. Slowdown factors (SDFs)                                              |    |

| 3.8.2. Hop count                                                            |    |

| 3.9. Energy consumption                                                     |    |

| 3.9.1. Effective Speed                                                      |    |

| 3.9.2. Frequency Co-Efficient                                               |    |

| 3.10. QUADRATIZATION OF THE PRODUCT                                         |    |

| 3.11. THE OBJECTIVE FUNCTION                                                |    |

| 3.12. SLACK RECOVERY TECHNIQUE                                              |    |

| 3.12.1. Makespan and slack                                                  |    |

| 3.12.2. Power consumption and slack                                         |    |

| CHAPTER 4: SCENARIO-BASED META-SCHEDULING (SBMES)                           |    |

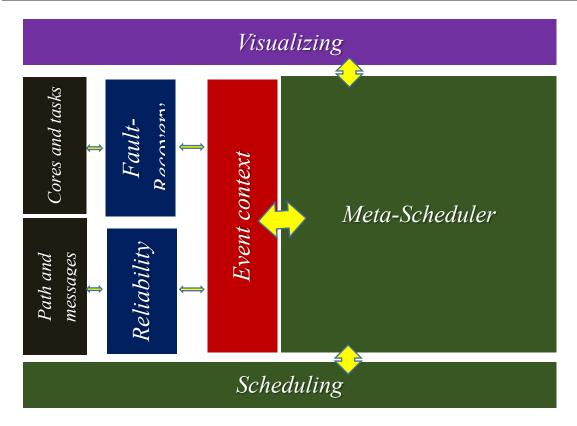

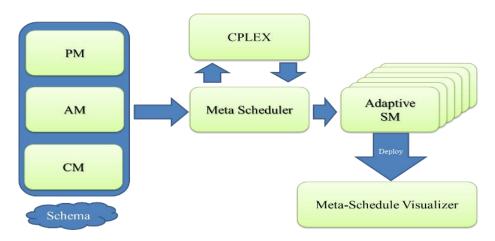

| 4.1. Meta-scheduler (MeS)                                                   | 63 |

| 4.2. SYSTEM MODEL AND ALGORITHM                                             |    |

| 4.3. ARCHITECTURE OF META-SCHEDULER (MES)                                   |    |

| 4.4. META-SCHEDULER (MES) DESIGN                                            |    |

| 4.4.1. Event-driving technique                                              |    |

| 4.4.2. The schedule model (SM) tree creator                                 |    |

| 4.4.3. Output generator                                                     |    |

| 4.5. FUNCTIONS AND ALGORITHMS                                               |    |

| 4.5.1. Main functions and algorithms                                        |    |

| 4.6. SCENARIO-RASED META-SCHEDLILING (SRMES) AND FAULT MODELING             |    |

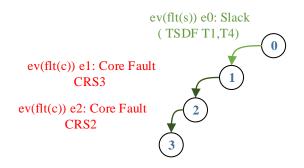

| 4.6.1. Fault assumptions                                                                 | 70    |

|------------------------------------------------------------------------------------------|-------|

| 4.6.1.1. Tolerance threshold range                                                       | 70    |

| 4.6.2. Fault-tolerant algorithm                                                          |       |

| 4.7. THE GOALS OF META-SCHEDULER (MES) DESIGN                                            | 72    |

| CHAPTER 5: VISUALIZATION AND EVALUATION OF SCHEDULES                                     | 75    |

| 5.1. REQUIREMENTS FOR BASIC VISUALIZATION                                                | 75    |

| 5.2. REQUIREMENTS FOR META-VISUALIZATION                                                 | 75    |

| 5.3. Graph mapping                                                                       | 75    |

| 5.4. GANTT MAPPING                                                                       | 76    |

| 5.5. VISUALIZATION OF SCHEDULE CHANGES                                                   | _     |

| 5.6. Energy calculation                                                                  | 77    |

| 5.6.1. Energy consumption                                                                | 77    |

| 5.6.2. Energy reduction                                                                  |       |

| 5.7. MEMORY AND META-SCHEDULES                                                           |       |

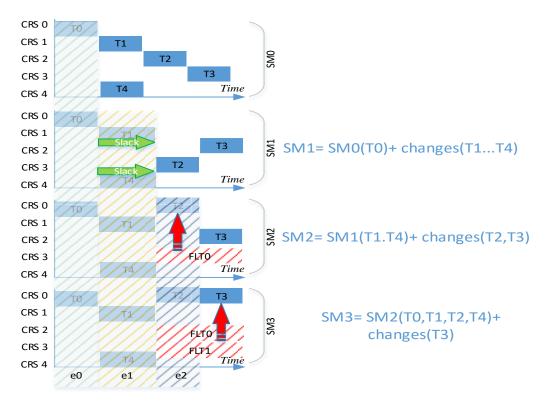

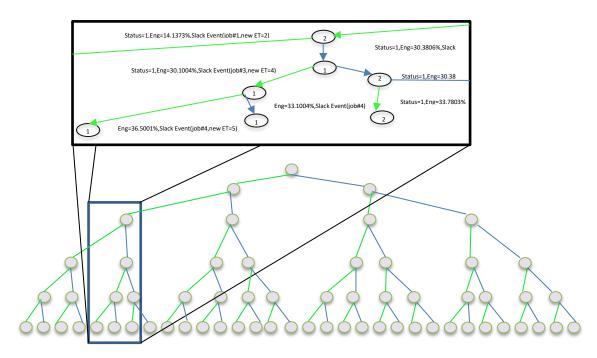

| 5.7.1. Convergence of meta-schedules for saving memory                                   |       |

| 5.7.2. Memory consumption                                                                |       |

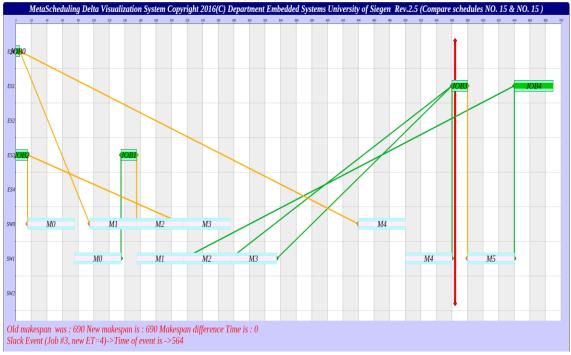

| 5.7.3. DELTA SCHEDULING TECHNIQUE AND DELTA TREE                                         |       |

| 5.8. Summary                                                                             | 82    |

| CHAPTER 6: IMPLEMENTATION                                                                | 84    |

| 6.1. SCHEMA MODELLING                                                                    | 84    |

| 6.2. IMPLEMENTATION OF THE DATA MODEL                                                    |       |

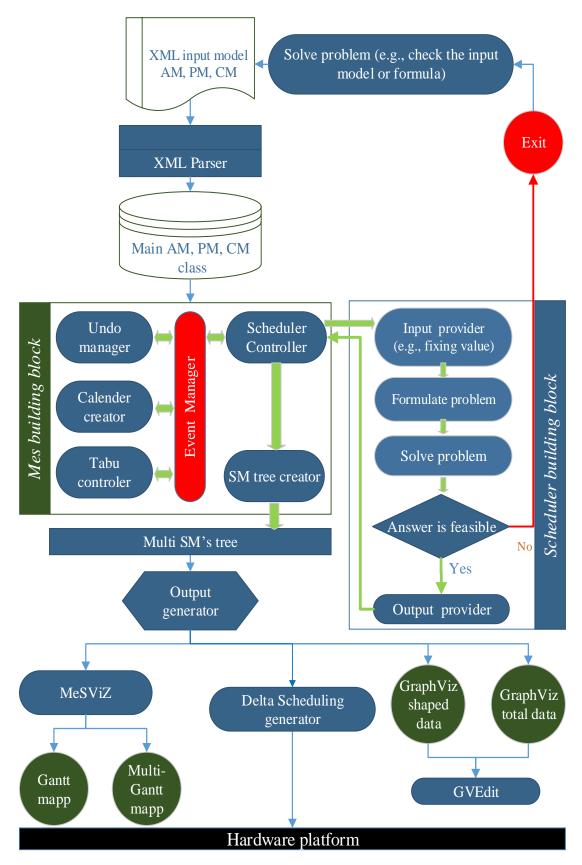

| 6.3. IMPLEMENTATION OF META-SCHEDULING (MES)                                             |       |

| 6.3.1. XML                                                                               |       |

| 6.4. IMPLEMENTATION OF META-SCHEDULING VISUALIZATION TOOL (MESVIZ)                       | 87    |

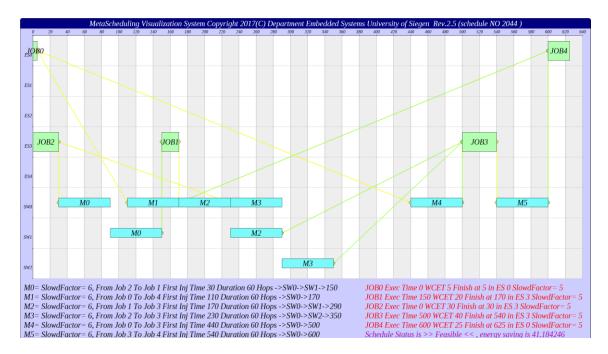

| 6.4.1. Outputs and formats                                                               | 88    |

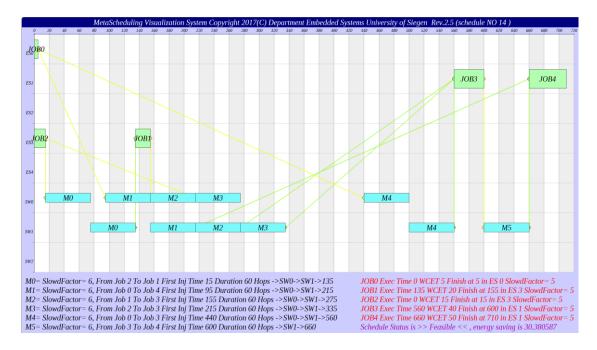

| 6.4.2. Single schedule Gantt mapping                                                     | 88    |

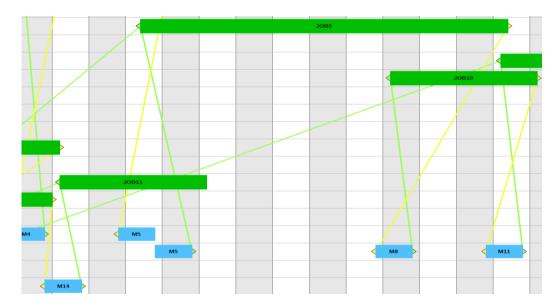

| 6.4.3. Multi-schedule Gantt mapping                                                      | 89    |

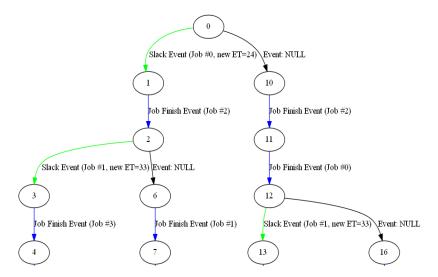

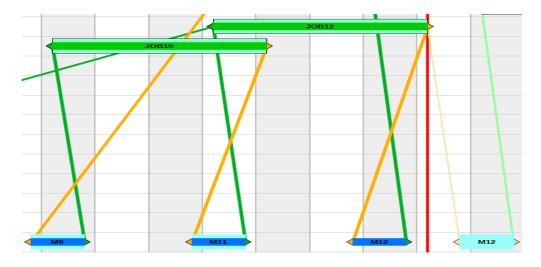

| 6.4.4. Graph mapping of meta-schedules                                                   | 89    |

| CHAPTER 7: EVALUATION EXAMPLE SCENARIOS AND RESULTS                                      | 91    |

| 7.1. EVALUATION OBJECTIVES                                                               | 91    |

| 7.2. VISUALIZING SCENARIO-BASED META-SCHEDULES FOR ADAPTIVE TIME-TRIGGERED SYSTEMS       | (TTS) |

|                                                                                          | 91    |

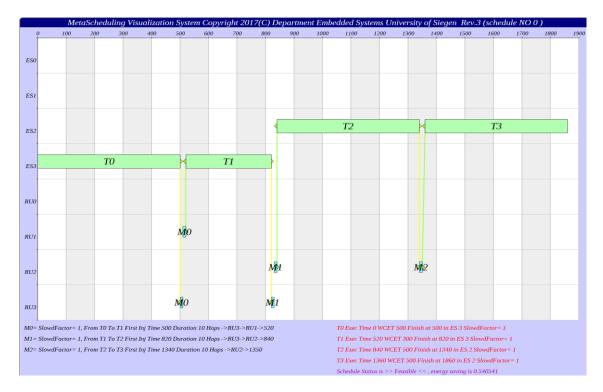

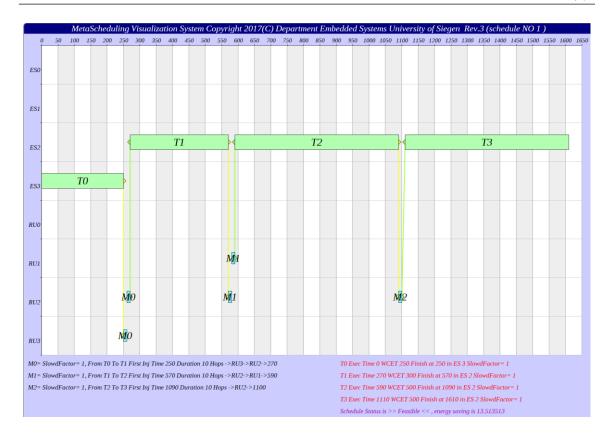

| 7.2.1. Simple model                                                                      | 91    |

| 7.2.1.1. Schedule model (SM) content                                                     | 91    |

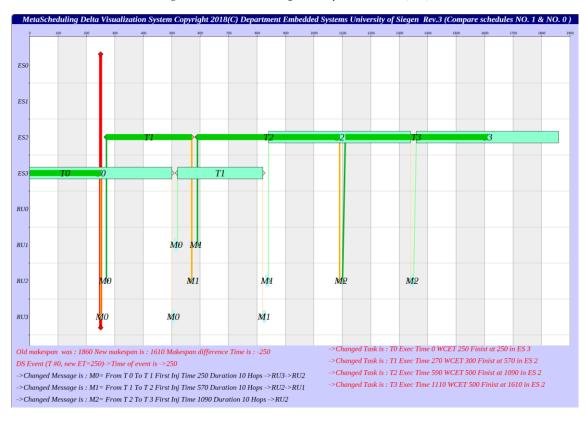

| 7.2.1.2. Output results                                                                  |       |

| 7.2.2. Complex model (CM)                                                                |       |

| 7.2.2.1.1. Schedule model (SM) content                                                   |       |

| 7.2.2.1.2. Output results                                                                |       |

| 7.2.3. Discussion                                                                        |       |

| 7.3. EVALUATION OF META-SCHEDULING (MES) RESULTS                                         |       |

| 7.3.1. Example 1 Sample scapping with four tacks and three massages                      |       |

| 7.3.1.1. Example 1. Sample scenario with four tasks and three messages                   |       |

| 7.3.1.2. Results for deta scheduling technique (BST) and deta tree (BT)                  |       |

| 7.3.1.4. Example 3. Big sample with $Ntsk = 9$ , $Nmsg = 8$ , and $Nssm = 512$ schedules |       |

| 7.3.1.5. Discussion                                                                      |       |

| 7.3.2. Scenario-based meta-scheduling (SBMeS) for frequency scaling of processors        | 103   |

| 7.3.2.1. Decision variables                                                              | 103   |

| 7.3.2.2. Slow-down factor                                                         | 103             |

|-----------------------------------------------------------------------------------|-----------------|

| 7.3.2.3. Objective function                                                       | 104             |

| 7.3.2.4. Input metadata for meta-scheduling (MeS)                                 | 104             |

| 7.3.2.5. Outputs and results                                                      | 105             |

| 7.3.2.6. Overhead                                                                 | 105             |

| 7.3.2.7. Discussion                                                               | 105             |

| 7.3.3. Scenario-based meta-scheduling (SBMeS) for frequency scaling of processo   | rs and network- |

| on-chip (NoC)                                                                     | 106             |

| 7.3.3.1. Scheduling constraints                                                   | 106             |

| 7.3.3.2. Decision variables                                                       | 106             |

| 7.3.3.3. Input metadata for meta-scheduling (MeS)                                 | 106             |

| 7.3.3.4. Outputs and results                                                      | 108             |

| 7.3.3.5. Discussion                                                               | 108             |

| 7.3.3.6. Overhead                                                                 | 110             |

| 7.3.4. Scenario-based meta-scheduling (SBMeS) for frequency scaling with flexible | e task-to-      |

| processor mapping                                                                 | 111             |

| 7.3.4.1. Input models                                                             | 111             |

| 7.3.4.2. Outputs and results                                                      | 112             |

| 7.3.4.3. Discussion                                                               | 112             |

| 7.3.4.4. Overhead                                                                 | 114             |

| 7.3.5. Scenario-based meta-scheduling (SBMeS) for improved reliability            | 115             |

| 7.3.5.1. Input models                                                             | 115             |

| 7.3.5.2. Outputs and results                                                      | 117             |

| 7.3.5.3. Discussion                                                               | 119             |

| 7.4. Summary                                                                      | 122             |

| CHAPTER 8: CONCLUSION AND FURTHER RESEARCH                                        | 124             |

| GLOSSARY                                                                          | 126             |

| LIST OF FIGURES                                                                   | 128             |

| LIST OF TABLES                                                                    | 131             |

| LIST OF EXAMPLES                                                                  | 132             |

| LIST OF ALGORITHMS                                                                | 133             |

| PUBLICATIONS AND PREVIOUS WORKS                                                   | 134             |

| I. REFERENCES                                                                     | 135             |

# Chapter 1: Introduction

Many algorithms, methods, and techniques are proposed for scheduling distributed embedded real-time systems. Schedulability analysis is a primary component of real-time systems scheduling. In particular, the real-time system depends on static schedules that define the use of computational and communication resources based on a global time base. In [1], Kopetz explains how the correctness of a real-time system also depends on the timing of the computational results.

A group of tasks and messages is said to be schedulable with a certain scheduling method if enough resources (e.g., cores, routers) are available to execute all these tasks and transmit all messages before their deadlines. Each real-time task and message is assigned a deadline, which is defined in an *application model (AM)*. In the time-triggered paradigm [1] of real-time scheduling, processes are controlled and scheduled by the progression of time only, and a schedule is designed for the total duration of a system's execution. One of the typical techniques used for *time-triggered systems (TTS)* is the schedule table. These are easy to verify and thus favorable in safety-critical systems that must be certified [2].

Scenario-based scheduling can support adaptive *TTS* by decreasing dependence on expensive and complex hardware, dynamic computational costs, and equipment vendor solutions and by replacing or reducing componential hardware functions with scheduling implementations on low-cost multi-purpose devices.

Energy-efficiency, energy-management, energy-saving, and energy reduction methods and algorithms are used in many applications (e.g., mobile phones, smart TVs), while their applicability in safety-critical systems is restricted.

**Network-on-chip** (NoC) technology contributes significantly to the overall energy consumption of an MPSoC, and we introduce a meta-scheduler (MeS) for SBMeS that supports dynamic voltage and frequency scaling (DVFS) in time-triggered NoCs and MPSoCs.

Some of the results and methods (e.g., meta-scheduling) described in this thesis are also used in the *SAFEPOWER* project platform and documents [3].

#### 1.1. Motivation

Embedded systems are pervasive in modern safety-relevant systems. They range from automotive electronics to aerospace flight control and multi-purpose complex aerospace vehicle systems; and many premium carmakers plan to invest heavily in e-cars, which significantly depend on embedded systems [4].

However, in the era of the IoT, the minimizing of power consumption is a primary concern for system designers. Scheduling optimization helps engineers and system designers to increase energy-efficiency and improve the behavior of a system [5].

Many embedded systems are based on *time-triggered networks (TTN)* and used in safety-critical applications (e.g., healthcare, e-cars, space, military, nuclear stations, and aircraft). Efficient scheduling algorithms and methods are required for such systems (e.g., mathematical programming, artificial intelligence, scheduling heuristics, neighborhood search [6]), where failure has severe consequences [7]. "Scheduling limited resources among requesting entities is one of the most challenging problems in computer science [8]".

In *SBMeS* systems, the MeS generates specific schedules for each situation triggered by relevant events (e.g., fault and slack). To evaluate schedules, system designers must design, model, compare, understand, debug, and simulate the schedules. These are the important challenges for *SBMeS*. Adapting to significant events within the computer system or in the environment is another challenge in *TTS*.

**NoCs** have emerged in recent years to improve performance and solve the challenges of existing interconnect solutions for many cores. **NoCs** provide a scalable and high-performance communication architecture for complex integrated systems.

Moreover, this solution tackles the challenge of power consumption, which is one of the essential concerns of complex embedded systems. Research findings indicate that the communication interconnect can consume up to 36% of the power required in an *MPSoC* [9]. This significant power consumption calls for low-power techniques for *NoCs*.

The output of most schedulers is in text format, making it difficult to identify problems, especially when a large number of schedules are generated and must be debugged or compared [10].

This challenge is intangible when using text logs with large amounts of data or abstract graphics that absorb the engineer's mental resources. The majority of the schedule visualizers are designed to illustrate a single schedule and cannot cover multiple schedules in one scope. However, the generation of schedules via scenario-based scheduling solutions and algorithms for real-time multi-processor systems is gaining importance [10]. The *MeS* approach is to add dynamic actions by computing several valid schedules, dynamically chosen based on the system status [11].

**SBMeS** is a scheduling technique [12, 13], which predicts, controls, and models the circumstance events in safety-critical systems. **MPSoC** systems typically represent one of the most power consuming components of embedded systems, and most research focuses on reducing power and energy consumption of computational cores. **MPSoCs** typically support the scaling of frequency and voltage (e.g., **DVFS**), as well as multiple sleep states for cores. However, frequency tuning for both cores and routers in multi-core architectures (e.g., **NoC**) has so far been an open research challenge.

In addition, energy efficiency and energy management are becoming important issues in real-time systems design [14]. One *NoC* design goal has emerged in the embedded and real-time systems market as a means of reducing and managing power consumption [15].

To deploy *TT NoCs*, static scheduling of application workloads is a prerequisite. In addition to ensuring application requirements, such as precedence constraints and deadlines, energy consumption is influenced significantly by task allocations and communication/execution plans [14].

Finding the optimum schedules for maximum energy reduction is the goal of the scheduling techniques presented in this work. This will result in better task allocations and communication plans. The scheduling algorithm extends previous work (e.g., [12], [14], [16]), introducing an energy reduction scheduling method for *TTS* [17]. Energy reduction is achieved via *DVFS* by *SBMeS*, a widely used technique that provides the support to reduce energy consumption of embedded systems and multi-core architectures.

Energy-efficiency in *DVFS* is achieved by dynamically adjusting the voltage, frequency, and performance settings of the application. To achieve the full advantage of the slack that results from variations in task execution time, it is important to recalculate the frequency and voltage settings during these periods (i.e., online).

Energy-efficiency optimization uses dynamic frequency scaling, in which we can individually scale the frequency of each core and router. This algorithm is suitable for mixed-criticality [18] and safety-criticality [19] by supporting fault-tolerant [20] applications and adaptive systems. Compared to static slack (SS) scheduling techniques, our approach provides more energy efficiency and enhanced flexibility.

The frequency is tuned for each component (core or router) and is optimized depending on the task or message, regarding events and the system global time.

However, optimal voltage and frequency scaling algorithms are computationally expensive and complex, if used at runtime. Therefore, to overcome and reduce online complexity, we propose quasi-static scheduling [21] for frequency scaling, supporting *TT* multi-core architectures. This method allows exploitation of dynamic slack (DS) and avoids energy dissipation due to online adaptation of the frequency settings.

Our method can support fault-tolerance and energy-efficiency, which are significant objectives in many safety-critical systems. Our algorithm considers the task execution times, message injection and transmission times, and possibilities of frequency changes

and can schedule and map the tasks and messages to be executed before the corresponding deadlines [22].

Our *SBMeS* model optimizes the trade-off between reliability, fault-tolerance, and energy-efficiency to handle multiple tasks and message sets regarding events (i.e., based on frequency tuning and scaling inside cores and routers). We consider the impact of each event on other events (e.g., increasing or decreasing frequency) for better resource and energy management in the *TTS*.

We present scheduling techniques for attaining the optimal schedules for different events with maximum energy reduction, while meeting other functional and nonfunctional constraints. A corresponding optimization problem is formulated in *IBM Ilog CPLEX*, and the results indicate significant improvements in energy efficiency.

In the e-car area, safety is one of the most critical parameters; hence, the fault-tolerant scheduling method used in *SBMeS* (cf. Section 4.6.1) can be applied in automotive systems to achieve greater safety.

In this work, slack occurrence is defined as an event. The required algorithm, methods, and scenarios are designed to support this event in improving energy-efficiency.

In many works, schedule results are explained by presenting the abstract text of the essential information (e.g., tasks, messages, makespan, deadlines, times).

A visualization of a schedule enables the engineers and system designers to easily perform sanity checks – checking and tracing the tasks, messages, makespan, nodes, and in *SBMeS*, the behavior and reactions for each scenario after an event. Although scheduling is an essential issue in *TTS*, embedded systems, and computer science, few visualization tools [8] are available to help engineers and scientists extend and develop more reliable scheduling algorithms, methods, and models [23]. Some visualization tools show only abstract schedules as graphical output and contain neither complete information nor detailed explanations of the events and the schedules (e.g., differences or changes) [7].

Comparing, understanding, and debugging thousands of schedules generated by *SBMeS* poses severe challenges for system designers, as discussed later in this work.

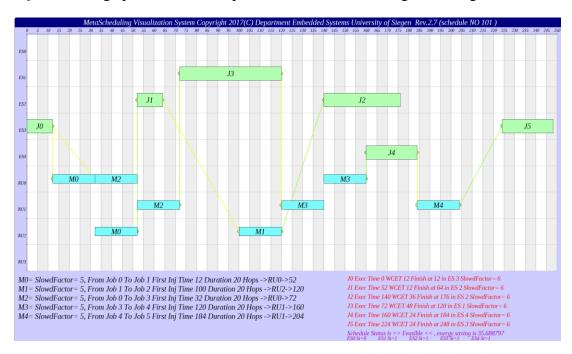

This work introduces a scenario-based tool, *MeSViz* – designed to support developers and engineers in evaluating scheduling algorithms, models, and methods for adaptive *TTS*. This tool can show event details and schedule changes and dependencies due to events. It visualizes schedules on four different layers: the first presenting individual schedules for each scenario, the second displaying multiple schedules for multi-scenario events, the third generating graphs, and the fourth showing energy and timing.

# 1.2. Research scope

This thesis presents *SBMeS* models and optimal algorithms and techniques, which can support adaptive *TTS* and reliability requirements for *MPSoCs* and *NoCs*. This thesis addresses *TTS* because the temporal interference between the cores and routers of *MPSoCs* and *NoCs* significantly complicates the analysis of *worst-case execution times* (*WCET*) [24].

The novelty contributions of this thesis can be summarized as follows:

- Scheduling of TT communication and computational activities: The scheduling

algorithm considers the task-execution times, message-transmission times and the

possibilities of frequency changes. Our scheduler supports the mapping and

scheduling of both tasks and messages to multi-core architectures, for minimizing the

total energy consumption regarding the timing and frequencies of cores, routers and

slack distribution.

- 2. **DVFS** in time-triggered architecture: This work enables the use of *DVFS* for both communication and computation resources for *MPSoCs*, in order to attain energy efficiency of *TT* multi-core architectures. Hence, it can extend energy efficiency optimisation of *SBMeS* for *MPSoCs* with time-triggered communication (TTC) not only providing frequency scaling of not only cores but also the *NoC's* routers.

- 3. *The scheduling method for improved reliability and fault-tolerance*: *SBMeS* can be used for automotive and safety-critical systems to achieve greater safety. In the e-car area, safety is one of the most critical parameters.

- 4. *Trade-off between fault-tolerance, reliability, and energy-efficiency:* Our proposed model optimizes the trade-off between fault-tolerance, reliability, and energy-efficiency in *SBMeS* to handle multiple tasks and message sets regarding reliability [20] and energy-efficiency for adaptive *TTS* (i.e., base frequency tuning and scaling inside cores and routers).

- 5. An optimal scheduling algorithm for energy efficiency: Our proposed optimization method establishes the minimum energy consumption for each slack event by mixed-integer quadratic programming (MIQP) equations. The MIQP model considers different parameters (e.g., cores, routers) and decision variables (e.g., slow-down factors of cores and routers) in the constraints and the objective function.

- 6. Visualization of meta-schedules: Our MeSViz is proposed for specific visualization and evaluation of single and multi-schedules on MPSoCs.

- 7. *Memory optimization regarding schedules size:* Delta scheduling is used to reduce and optimize memory usage of schedules and can store a significant number of schedules based on delta graph generator models [25], [16].

In contrast, our approach is an off-line static-scheduling algorithm for determining the optimal meta-schedules and dynamic frequency scaling in *TT MPSoCs* and *NoCs* for energy-efficiency in safety-critical embedded systems. This work thus develops a DS - reclamation technique to reduce static and dynamic energy consumption.

#### 1.3. Structure of the thesis

The remainder of the dissertation is structured as follows:

**Chapter 2** analyses the literature, related and previous works, basic concepts, and the current state of the art. In section 2.8, we compare this work with related works in two tables to clarify the research gap.

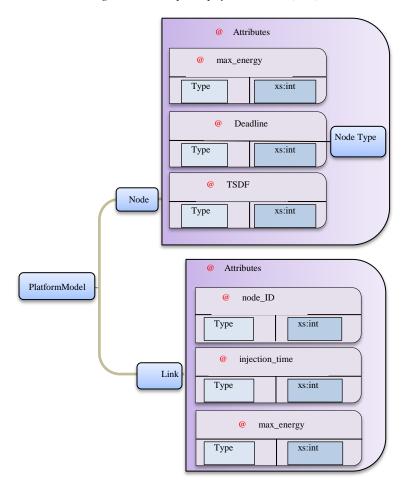

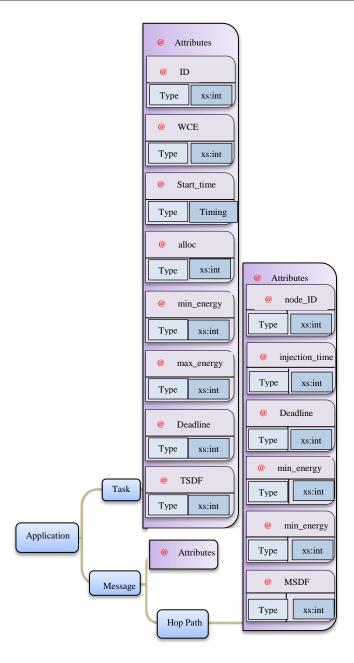

**Chapter 3** introduces the scheduling model for the adaptive *TT* and safe and mixed-criticality systems. Our model supports the static scheduling for *TTS* and creates specific data models for physical (hardware), application (logical), and context (scenarios and events) layers. The general definitions, energy model, and objective function are then distinguished (e.g., constraints and variables).

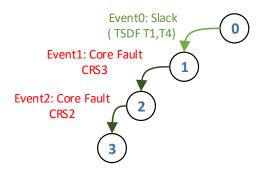

**Chapter 4** provides a detailed description of our specific *SBMeS* technique, algorithm, and developed tool (*MeS*). The system model and algorithms, architecture, and fault assumptions are then distinguished.

**Chapter 5** presents the techniques for visualization, evaluation, and convergence of schedules. It presents our specific meta-scheduling visualizing technique and the developed tool (*MeSViz*).

**Chapter 6** concerns the implementation. In this chapter, we provide information about the schema model, based on standard *XML* as an input. The implementation of *MeS* and *MeSViz* and outputs are explained.

**Chapter 7** presents the evaluation of the scenarios and models. In this chapter, we provide different scenarios and use cases for energy-efficiency (cores and communication network), energy-efficiency with fault-tolerance, and saving memory. In addition, the results are evaluated and visualized using *MeSViz*.

**Chapter 8** concludes the dissertation and suggests an outlook for future work on *SBMeS* on adaptive *TT* and mixed-criticality systems.

# Chapter 2: Related work and basic concepts

In this section, we begin with basic concepts and review the ideas of related works in the area of real-time systems, *TTS*, energy management, scheduling, and visualization; then briefly introduce our previous works [10, 12, 13]. In heterogeneous embedded systems (e.g., *MPSoC*), many elements are used (e.g., CPU, GPU, and *NoC*) and they must be designed, developed, and operated to satisfy the reliability and performance requirements of safety-critical embedded-systems applications. *MPSoCs* are increasingly popular, which they are using high computational power and low power consumption embedded systems.

### 2.1. Real-time systems

A real-time system must execute concurrent tasks and messages in such a way that all tasks and messages meet their specified deadlines. Communication and task deadlines are significant constraints that a scheduling algorithm for *RTES* must satisfy in addition to optimizing energy-savings [22].

### 2.1.1. Embedded real-time systems

In general, opinion about the real-time system is often considered to be implemented through an embedded system platform [23].

Figure 1. Conceptual difference [23]

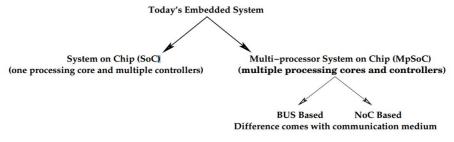

In Figure 1, the embedded system and real-time system are strongly correlated, but there are applications and areas where this correlation is not observed [23]. However, this does not concern a difference between two different systems, but rather a new vision of the application of two systems in a single scope. Figure 2 represents the embedded system situation and the new scope of its additivity.

Figure 2. Current and future trend in an embedded system [23]

#### 2.1.1.1. Makespan

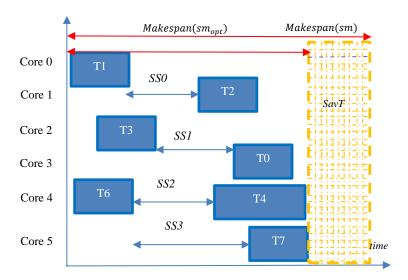

In [26], Eitschberger et al. present a scheduling model to balance faults and energy to maximize the performance in static schedules. However, it is vital to minimize the time length of a schedule (the so-called *makespan* [27]): in effect, the duration until all tasks have finished processing, while integrating fault tolerance techniques. They propose that one of the recently emerging topics is the problem of minimizing energy consumption by *NoCs* [26, 28].

For example, ignoring the possibility of slack recovery is regarded as wasting energy. Energy consumption is also affected by the frequency scaling of cores and routers. By increasing the execution time via decreasing the clock frequencies in cores, the length of the makespan also increases. Fault-tolerance techniques typically result in performance overhead, which leads to an increase of the makespan.

However, decreasing the clock frequency also decreases energy consumption. This mechanism leads to a two-variable trade-off decision between performance and energy consumption, on both cores and routers.

#### 2.1.2. Dependability

One of the most critical non-functional parts of real-time systems is *dependability* [29], which is the ability of a real-time system to provide its agreed level of service to its application [30]. According to [29], the  $IEC/IEV^1$  191 – 02 – 03 has a specific description: "Dependability is the collective term used to describe the availability performance and its influencing factors: reliability performance, maintainability performance and maintenance support performance." According to [31], the conceptual structure of dependability comprises three important components, which are faults, means, and attributes of dependability. In this work, we focus on faults.

## 2.1.2.1. Mixed-criticality systems

Safety and reliability in *mixed-criticality systems (MCSs)* (e.g., vehicles, airplanes, drones) and their standards (e.g.,  $ISO\ 26262$ ,  $IEC\ 61508$ ,  $DO\ -\ 178B$ ,  $DO\ -\ 254$ , and  $ISO\ 26262$ ) are the primary focus of many works [32].

However, the current tendency is to increase integration, build safer and more reliable complex or large embedded systems. These systems requirements commonly refer to *MCSs* [33]; that is, including two levels: safety critical (high criticality) and mission-critical (low criticality). It is crucial for tasks to meet the requirements for criticality levels [34]. There can be up to five levels of standards [32].

Isakovic et al. [35] explain that physical component designs and interfaces with a specific computer system should provide a clear design methodology approach, but systems become more complex primarily when working with heterogeneous systems and

<sup>&</sup>lt;sup>1</sup> International Electrotechnical Commission

protocols. However, it is challenging to ensure that the functional properties meet the system specifications and regulatory guidelines. The authors also offer a mixed-criticality integration solution based on a *TTA* for a hybrid system-on-a-chip platform.

The *SBMeS* algorithm is designed for static scheduling because dynamic scheduling has more complexity and is typically not amenable to certification.

Our algorithms and tools, used in [12, 13, 36], are extended with support for frequency scaling in a *TT* multi-core architecture. This technique can also be used for *TTS* with mixed-criticality [19], while meeting requirements for adaptivity, energy efficiency, and fault-tolerance, as in [25]. For example, *SBMeS* enables reactions to fault events by preplanning for each event and fault, with a recovery strategy via static scheduling. In many safety-critical real-time systems, fault-tolerance and energy-efficiency are essential objectives [33].

# 2.1.3. Adaptivity

The design and development of embedded systems is driven by the constraints of certification standards [19]. While these standards advocate static resource allocations [37], adaptivity is also desirable for fault recovery and energy-efficiency [38]

Safety-critical systems are vital and sensitive, and any failure can have a significant effect on people or cause damage to the environment.

Recent technology trends favor the adoption of multi-core architectures with *NoC* for safety-critical applications [39]

In addition, *TTNoC* [40] and AEthereal [13] effectively support the fault isolation and predictability requirements of safety-critical systems. Time-triggered control is a valuable solution for safety-critical systems to manage the complexity and provide analytical dependability and timing models.

This work addresses adaptivity in *TTS* by deploying multiple precomputed schedules and routering between such schedules at runtime.

# 2.2. Time-triggered systems (TTSs)

According to [17], a real-time system is defined as one in which the correctness of its behavior depends on computational results as well as the physical time in which these results are produced concerning the global time base. In *time-triggered architectures* (*TTA*), activities are triggered by the progression of global time.

By dedicating a priori defined bandwidth to *TT* messages, timely delivery of all messages is guaranteed.

#### 2.3. Global time base

In *TTS* architectures, activities are triggered by the progression and control of global time [17].

### 2.3.1. Time-triggered networks (TTNs)

TTNs (e.g., TTEthernet and FlexRay [41]) are advantageous in safety-critical systems for managing the complexity of fault-tolerance and analytical dependability models (TTEthernet is currently under standardization by SAE as AS6802 [42]) [13]. In addition, TT architectures in NoCs, such as TTNoC [40] and AEthereal [43], support the fault-isolation and safety-critical requirements.

In-vehicle network protocols (e.g., FlexRay, Local Interconnect Network (LIN) [44]) use the *TT* pattern, the time of which is divided into communication cycles.

### 2.3.1.1. Messages

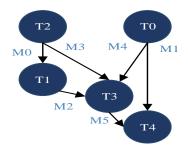

Once a task finished, data or an information packet is sent to the next dependent task, which this packet called message. Each message is scheduled for routing, sending, and receiving with the timing determined according to the tasks and messages dependency and to avoid message collisions in path links and routers.

# 2.3.2. Time-triggered multi-processor system-on-a-chip (MPSoC) and network-on-a-chip (NoC)

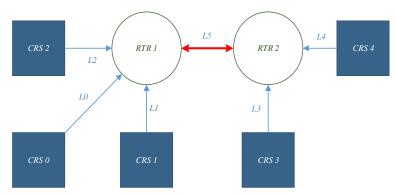

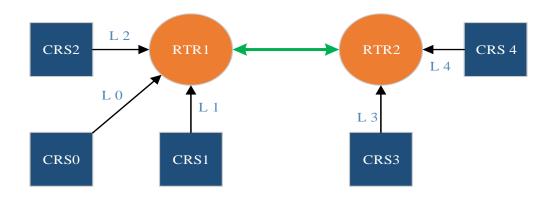

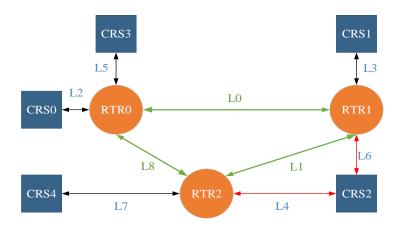

**MPSoCs** in heterogeneous systems include many elements (e.g., CPU, GPU, Cache, SRAM, FPGA and **NoC**) [45]. With latency-sensitive applications running on such **MPSoC** platforms, the cores and routers must be designed and operated to satisfy the performance requirements. **DVFS**, adaptive routing, and frequency scaling in routers and links can potentially improve energy efficiency and performance of the **NoC**.

An *MPSoC* can be viewed by its physical and logical viewpoints. Physically, the platform consists of cores interconnected by a *NoC*.

The message-based services of the *NoC* enable the abstraction from the internal implementation details of the cores, which can range from state machines in hardware to full-scale processors with operating systems and application software.

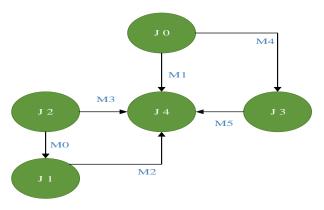

An application on an *MPSoC* can be described by a *directed acyclic graph (DAG)* [46], where tasks are connected by edges to represent data dependencies. An edge between two tasks represents a service required by the destination task. For example, the computation of set values in a "controller task" depends on sensory data from an "I/O task" providing information about actual and desired values.

Spatial and temporal allocation of the elements from the logical view of the physical platform is required before execution begins. Tasks are mapped to suitable cores, while message-based services are mapped to paths and time intervals on the *NoC*. Likewise,

router configurations must be coordinated in such a way that the routing decisions prevent collisions.

Another advantage of using *NoCs* is the effective support for multiple clock domains, which is particularly important for the proposed concept in this work. It is essential to support the clock domain [47] crossings [48] for the proposed DFS [49] technique to reduce the system's power consumption.

**NoCs** are composed of three main building blocks: links, **network interfaces** (**NI**), and routers. Links serve as a physical connection between cores, routers, and **NIs**. The **NI** is an interface that makes a logical connection between the cores and the network. The routers send and receive the packets, which are delivered by the other routers or cores through the **NI**. Consequently, routers are responsible for sending the packets to the right destination, using the destination address included in the packet.

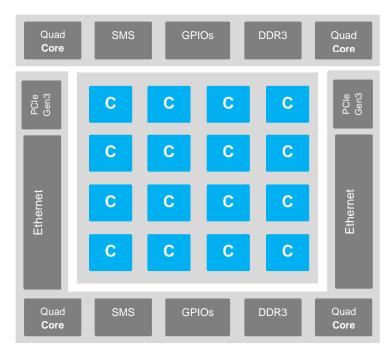

**NoCs** are composed of three main building blocks: links, **NI**, and routers. More cores typically means higher power consumption: including more cores thus presents a design hurdle of architectural complexity and higher energy consumption. For example, the **Kalaray MPPA2-256** [50] comprises 288 cores: 256 computing cores, 16 management cores, and four quad cores (see Figure 3). **Kalray's MPPA** [51] technology addresses these challenges by combining high-performance cores with low-power processors [52].

Figure 3. Kalray's MPPA network-on-chip (The MPPA2® - 256 Bostan2 processor [52])

Many *MPSoCs* are based on complex communication infrastructures similar to *NoCs* (e.g., Samsung Exynos, Multicore *DSPs*, and *many-core Kalray MPPA*). Using *NoC* for the implementation of the proposed concept is essential as *NoCs* make the interconnected elements independent of the clock frequency. More precisely, buffers between different components can be used as clock segregation boundaries if different frequencies are

demanded. Moreover, a routing algorithm is required to route the messages to the right destination.

In a real-time system [53], the correctness of its behavior depends on the values and the timing of computational results. Therefore, it is a beneficial solution in safety-critical systems to manage the complexity of analytical dependability and timing models.

## 2.3.3. Time-triggered (TT) execution environments

**Real-time operating systems (RTOS)** are used in embedded systems where time is a vital parameter and function; also RTOS needs to control and serve many resources requirement (e.g., core, memory). For example, **XtratuM** is a hypervisor based on **RTLinux HAL** to meet safety-critical real-time systems requirements. These **RTOSs** or hypervisors are supported by specific standards for specific use cases (e.g., ARINC 653 for avionics) [54].

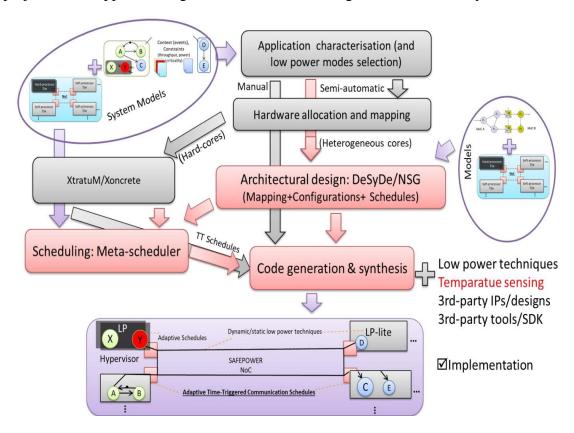

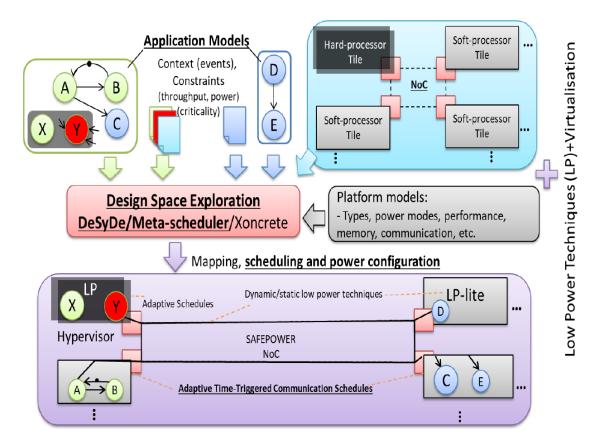

Figure 4 shows how the Xtratum [55]/Xoncrete [56] design from the *SAFEPOWER* project can be applied, along with the meta-scheduling for the hard-core system [3].

Figure 4. Simplified design flow and meta-scheduler (MeS) integration in SAFEPOWER [3]

#### 2.3.3.1. Tasks

Applications or processes that is running on a core called to task. These tasks require a schedule for timing and allocation regarding priority, coherency, and/or dependency.

## 2.3.3.2. Worst-case execution time (WCET)

The *worst-case execution time (WCET)* of a task is pre-estimated or pre-computed as an input for scheduling. However, this determination is difficult to achieve.

#### 2.3.3.3. Slack

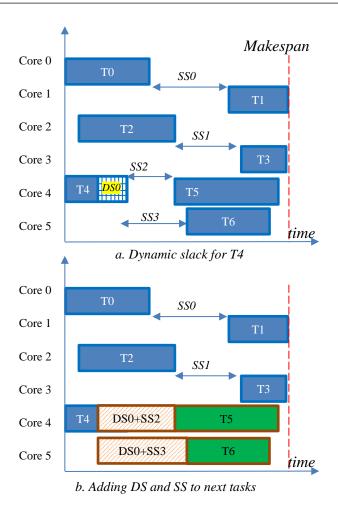

The SSs happen when the system is under loaded, and DS occurs when it finishes faster or earlier than predicted *WCETs*. Finally, DS can provide space for other tasks to be executed [34].

We further note that the execution time variations sometimes leads to DS time [57], which can be exploited by different levels of *WCET* and changed without causing a performance penalty. In this work, we use the slack time in cores to reduce energy consumption.

#### 2.4. Energy management techniques

# 2.4.1. Clock gating and power gating

Clock gating and power gating are the well-known, general techniques for reducing power dissipation and energy management in hardware systems. Clock gating with logical techniques reduce clock power using a circuit to prune the clock tree [58]. Power gating is designed to shut off the circuit not in use and to increase time delay [59].

## 2.4.1.1. Dynamic voltage and frequency scaling (DVFS)

One of the most famous and prevalent run-time techniques for improving power efficiency is *DVFS* [60]. *DVFS* techniques are widely used for scaling and optimizing power [60], providing a solution in which the chip's voltage-frequency levels are varied at run-time [15].

In this work, *DVFS* is used to establish an optimized frequency for each core. The power efficiency of *DVFS* is primarily related to the performance of the slack estimation method [61].

Embedded systems use some well-known, energy-efficient techniques [62], including *DVFS*, to improve energy-saving and the power-efficiency of chips at run-time [63].

Bianco et al. [64] analyzed a similar problem, concerning **DVFS** on **NoC**, focusing on single voltage, single frequency, and links working at a single frequency. They considered only the **DVFS** related to the data transmission, due to the bit switching activity, and their simulation results did not consider or include the flit queueing effects and the contentions due to routing.

Caria et al. [65] show that a combination of fine-tune energy router hardware (akin to *DVFS*) and *traffic engineering (TE)* in the network enables most energy savings. Their case study suggests that the energy savings of *DVFS* vary between 25% for highly utilized networks and 50% for lightly loaded networks.

# 2.4.1.1.1. Frequency tuning on network-on-chip (NoC)

In the literature [66], *DVFS* is one of the best known energy-efficiency techniques for improving power efficiency of chips at run-time [15]. We also use *DVFS* to establish optimized frequencies for cores and routers.

Chai et al. worked on a combination of execution time, *DVFS*, slack time, and power consumption to find energy-efficient schedules with minimized processor frequencies [67].

An *NoC* provides the different network interconnection models between *processing elements (PEs)* through routers. It can permit hop-by-hop communications between *PEs*. To serve and provide higher traffic demands in *NoCs*, *PEs* and routers run at higher clock frequencies. Therefore, "power consumption grows rapidly and limits *NoC* scalability" [64].

The use of *DVFS* to increase power efficiency of the *NoC* can be implemented on different levels (i.e., at the router level or the NI level). However, in this work, the *NI* serves as a platform for handling DVFS by supporting different schedules provided by the MeS, making the routers simpler and with low overhead.

# 2.4.1.1.2. Distributed dynamic voltage and frequency scaling (DVFS) algorithm at the router and core level

Sharma et al. [68] propose the communication energy technique, similar to the optimal solution obtained by *integer linear programming (ILP)*, as a low complexity heuristic mapping algorithm.

However, few platforms can support full stage DVFS at the router and interconnection level. For example, in  $Xilinx\ ZYNQ-7000$ , the input clock is 100 MHz and the PL fabric clocks generated on the software side are equal to 85 MHz and 170 MHz [69].

Some simulations and models are proposed as a scalable power-gating technique for reducing energy consumption. For example, Farrokhbakht et al. [70] worked on a scalable mapping and routing technique (SMART), which results in SPLASH-2 benchmarks that show it can decrease the static energy and average packet latency of the *NoC* network by 27.3% and 49.9%.

# 2.4.1.1.3. Worst case execution times (WCETs) and distributed dynamic voltage and frequency scaling (DVFS)

**WCET** is the maximum execution time of a task, which is pre-estimated or pre-computed and uses analytical or measurement-based techniques. **WCET** is an essential input for scheduling in **TTA**.

Our approach is driven by certification requirements and is based on an off-line and static-scheduling algorithm to compute the optimal meta-schedules and dynamic *SDFs* for

more energy efficiency. It addresses the DS reclamation scheduling technique to minimize static and dynamic energy consumption.

In this work, we use slack distribution to achieve power efficiency with scenario-based schedules containing different *SDFs* for *DVFS* in both cores and routers.

# 2.5. Energy management for different types of resources

## 2.5.1. Network-on-chip (NoC)

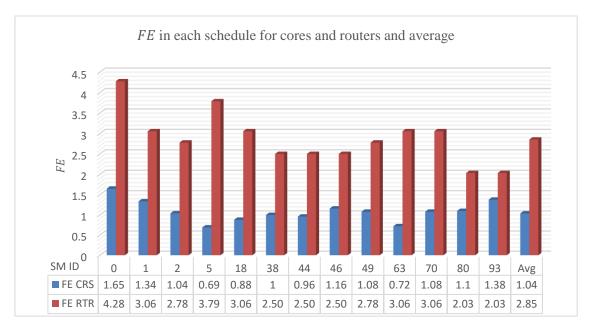

*NoCs* enable scalable communication for connecting several resources within a chip (e.g., routers). Energy consumption is primarily by computing (i.e., cores) and communication (e.g., routers) [71] and can contribute considerably to total chip power. For example, on-chip routers and links consume up to 18% in the Intel SCC and 20% in the Alpha 21364 processor and communication power takes 33% in RAW architectures [14].

Sheikh et al. investigated the combined optimization of *performance*, *energy*, *and temperature* (*PET*) [72] and propose an optimization framework. They assessed multiple cores for frequency switching.

Jingcao Hu et al. [73] used static schedules for communication and computation of tasks on heterogeneous *NoC* architectures for multimedia. Their algorithm achieved approximately 44% energy on average, compared to the standard earliest-deadline-first scheduler.

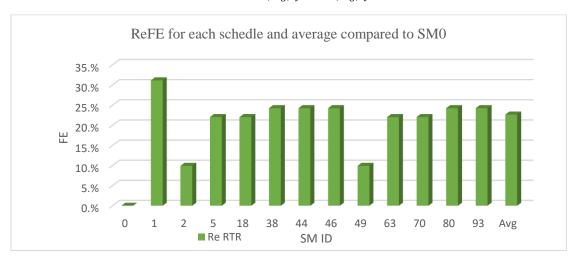

Various power saving techniques have emerged for *NoCs* at system-, architecture-, and circuit-level [74]. Experimental results indicate that slack algorithms can reduce energy consumption by 20~50% [75] more than existing *DVFS* algorithms [61].

In [76], the experimental results indicate that a dynamic SDF, on average, has 10% energy gains over static models.

In [73], the authors provide energy-efficient scheduling with static schedules for both communication activities and computational tasks in heterogeneous *NoC* architectures, under real-time systems constraints and for a multimedia application.

The algorithm achieves a 44% energy reduction, on average, compared to the standard earliest-deadline-first scheduler. In addition, scenario-based scheduling methods are presented.

In [77], the authors identify a relationship between execution time, DVFS, slack, and energy consumption, achieving energy-efficient scheduling with lower processor frequencies. They report that 28%  $\sim$  36% of the total chip power consumption depends on NoC energy consumption (e.g., on-chip routers and links).

In [78], it is observed that the low power technique reduces energy consumption in an average *NoC* by 49%, with negligible effects on network bandwidth and delays.

In [79], the authors used *voltage/frequency scaling (VFS)* and propose a power-efficient network calculus-based technique to minimize the power consumption of the *NoC*, which can save up to 50% of the total power consumption.

Han et al. [80] present a low power methodology and routing algorithm for temperature to achieve an ultra-low-power *NoCs*. The experimental results demonstrate an average power reduction of 36% over 21 applications.

Li et al. [81] propose a two-step solution for the problem of energy-efficient mapping and scheduling in *NoCs*. They used quadratic binary programming to minimize the communication energy and a genetic algorithm to minimize the overall system energy consumption.

#### 2.5.2. Processor

Lee et al. [61] [82] worked on a method of DVFS-enabled multi-cores to reduce energy consumption by executing the tasks in parallel on a sufficient number of cores and assigning the lowest possible frequencies. Their scheme saves up to 67% of the energy when executing the task on a single core. However, it does not support scenario-based scheduling and communication frequency scaling.

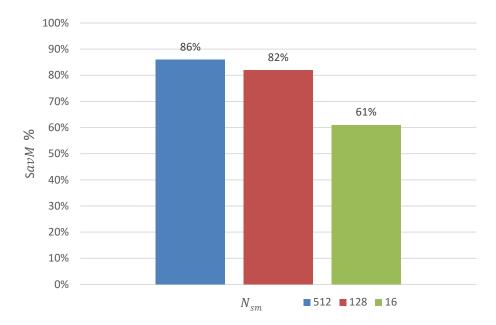

Related work indicates that slack-algorithms for DVFS [61] are valuable methods of reducing energy consumption by 20~50% [75]. In [76], the results indicate that a dynamic *slowdown* for cores, on average, results in 10% energy gains over static models. In [13], the results show that a DS algorithm for cores, compared to the SS, produces a maximum of 64.4% energy savings in a single schedule and 41.61% energy savings on average.

Hangsheng et al. found that the communication interconnect can consume up to 36% of the power in an *MPSoC* [9].

Also, compared to the related works in case of energy, we use optimization techniques for adaptive routing and frequency scaling in cores, routers, and links which can potentially improve *MPSoCs*' energy-efficient performance. The potential of DVFS for the router is interesting and our *SBMeS* could extended for this.

## 2.5.3. Task procrastination and slack reclamation

Using reclaim the SS or DS in traditional real-time systems is not a new practice (e.g., Sprunt et al. [83], Strosnider et al. [84]).

Chatterjee et al. [85] take the slack time [76] of tasks into account to improve deadline satisfaction and reduce energy consumption. They propose an algorithm for fault-tolerant resource allocation in real-time dynamic scenarios. On average, they reduced energy consumption by 29.1% and 6.7%, compared to previous work.

In [76], static and dynamic task procrastination is introduced as a slack-reclamation technique for energy reduction over the static task *SDF*. Their simulation found that dynamic *SDF* results on an average of 10% energy gains over the static *SDF*.

Dynamic procrastination reduces idle energy consumption by 15%, while meeting all timing requirements. Mahapatra et al. [86] propose an energy-efficient slack distribution technique for multimode distributed real-time systems. Their work provides a network traffic monitoring technique and a slack distribution mechanism to achieve power efficiency. A co-simulation framework was used to evaluate their proposed technique.

The relationship between execution time and energy consumption for energy-efficient scheduling is presented in sections 3.9 and 3.12, and this shows how *DVFS* is used for slack times between tasks to save energy with lower processor frequencies.

#### 2.6. Scheduling for time-triggered systems (TTS)

Message and task scheduling are problems for *MPSoCs* that are solved using TT scheduling. In task scheduling, the scheduler must decide when and where a task is to be executed, using each cove in every time slot.

The static TT schedule determines that TT messages through which link must be sent over the network at the predefined timing, deadlines and how the messages reach their destination before a global timeout.

In this work, message and task scheduling are related, and we focus on these aspects of the system because these problems and their associated constraints (energy-efficient, reliability, and fault) are an interesting component of previous associated works, which have produced valuable and positive results [85, 87].

# 2.6.1. Algorithms for static

Nowadays, many different techniques, algorithm, and methods are using for synthesis and generating the TT schedules (e.g., GA, constraint programming (CP) [88] ILP, MIQP, and satisfiability modulo theory [89]).

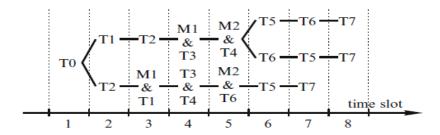

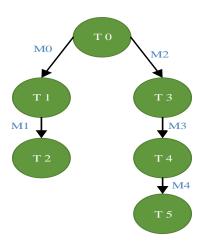

In static or pre-runtime scheduling, a feasible schedule for a set of tasks is calculated offline and pre-compiled [17] which was generated before run-time. The scheduling technique has to guaranty all deadlines, considering the resource, precedence, synchronization requirements for all tasks and conditions [17]. In scheduling the precedence relations between the tasks and messages, executing in the different nodes and events can be depicted in the form of a precedence graph [17]. For scheduling a problem, "a solution can be detected as a finding a path, a feasible schedule, in a search tree by applying a search strategy [17]" Figure 5.

Figure 5. A search tree for time slot [17]

Static-scheduling is a reliable solution for robust and timely systems, especially in *TTS*. Their scheduling problem was established by formulating a *mixed-integer linear programming (MILP)* problem.

Murshed et al. [90] have provided a static message-based scheduling approach that guarantees the absence of collisions in message routing for a single task per core. Their solution of the MILP problem is the allocation of tasks to cores and scheduling the messages between these allocated tasks while minimizing the critical path delay.

One of the Boolean problem [87] in scheduling is a synthesis of *TT* schedules; namely, when a schedule calls the correct schedule, it must meet all its requirements, otherwise it is incorrect. However, the other problem relates to the quality definition, with finding, choosing, and rating high-quality schedules being an interesting problem for new research. However, the "quality" is a complex and varied concept that can change quickly, according to context.

Wang et al. [91] worked on heuristic static task scheduling for performance yield maximization in *MPSoC*. This assigns tasks to cores, working from the root node to the end node of the task graph until all tasks are scheduled.

Mirzoyan et al. [92] worked on heuristic variation-aware task scheduling methods, using data flow graphs. This was limited to real-time streaming applications, with a *synchronous data flow graph (SDFG)* [93] model that does not support fault-tolerant and energy-efficient.

# 2.6.1.1. Static scheduling for energy efficiency

Energy efficiency, energy management, and energy reduction are essential issues in embedded systems. Many real-time systems must adapt to run-time critical events, such as faults inside or outside the system and environmental conditions.

The authors of [22] worked on an algorithm for task scheduling and time constraints where task deadlines were satisfied, saving more energy without degrading performance.

The authors of [73] developed energy-aware scheduling, search, and repair, with their model guaranteeing the prevention of missed task deadlines. This is also considered in this work.

# 2.6.1.2. Static scheduling for reliability

The use of the *TT* scheduling method for embedded systems is compelling because it provides predictability and greater safety and reliability. Some related mode switched scheduling techniques are proposed in the literature (e.g., Burns and Davis [33], Hu et al. [34], Baruah et al. [94], Burns and Baruah [95], and Ekberg and Yi [96]).

Guy Avni et al. [87] worked on *TT* schedules for switched networks with faulty links. They addressed the problem of the resistant schedule and propose how one can use the fixed error-recovery protocol to guarantee messages arrive at their destinations, regardless of which links failed. They focused on two *TT* scheduling limitations. The first is the computational constraints and variables complexity of synthesizing, named an *NP*-complete problem [97].

#### 2.6.2. Meta-scheduling (MeS) and mode changes

Most *TT* systems and *TTN* schedules are generated offline (static scheduling), but when the application or hardware model changes, most schedules cannot support events and their recent change. For example, since the systems using *TTN* or *TTS* are usually safety-critical, events and changes caused by the link, router, and core failures complicate scheduling tasks and messages [98].

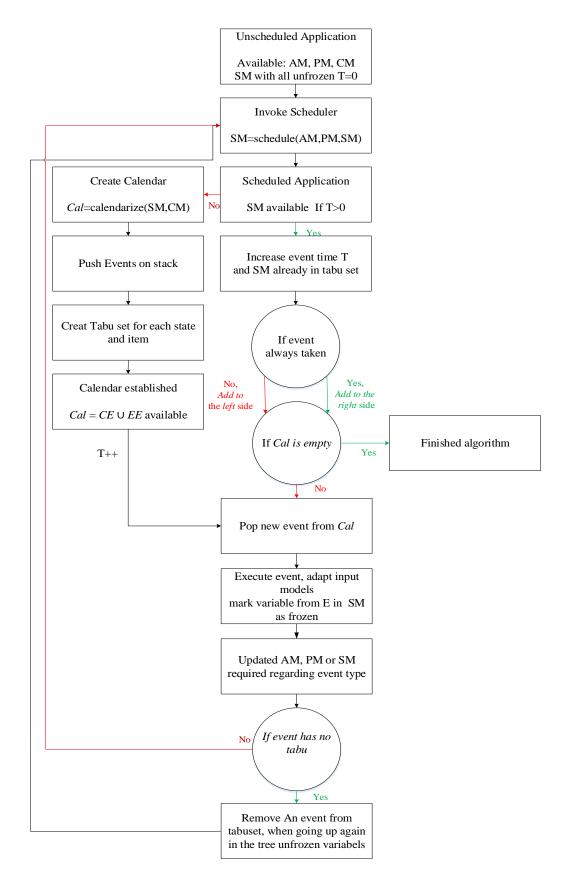

Quasi-static scheduling supports adaptive behaviors to reduce system costs when a limited number of predefined cases in scenario-based systems occur. The quasi-static scheduling technique is restricted to dynamic reactions and activities, while having very limited scheduling overhead.

Most of the research on meta-scheduling is conducted for enterprise grids, clouds, and data centers; for example, GridWay,<sup>2</sup> community scheduler frameworks,<sup>3</sup> Moab cluster suite,<sup>4</sup> Maui cluster scheduler,<sup>5</sup> DIOGENES, and synfiniWay's meta-scheduler [11].

However, Jung et al. [99] worked on meta-scheduling for green computing to reduce energy consumption and thus reduce  $CO_2$  emissions into the atmosphere. This approach is known as "GreenMACC." Following many rule changes in the EU concerning green and pure energies, and aimed to benefit the environment by reducing fossil fuels and controlling greenhouse gas emissions (e.g.,  $CO_2$  [100]). To this end, for example, BMW, Bosch, and Continental invested in battery cell [101] and most carmakers plan to invest heavily in research and development in the domain of e-cars, which depends significantly on embedded systems [4].

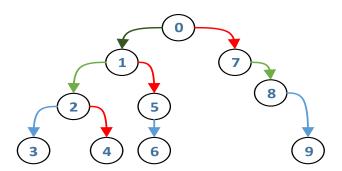

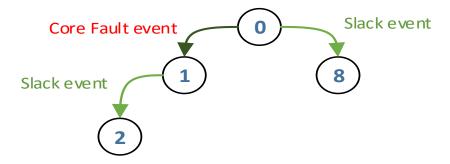

In [102], Fohler presents a method for supporting schedule changes based on operational modes, by switching and traversing static-schedules in a schedule status tree.

Jung et al. [103] worked on *synchronous data flow*, which is commonly used in signal processing or streaming applications. Their model can be used for dynamic behavior

<sup>3</sup> http://toolkit.globus.org/toolkit/docs/4.0/contributions/csf/

<sup>&</sup>lt;sup>2</sup> http://www.gridway.org

<sup>&</sup>lt;sup>4</sup> http://www.adaptivecomputing.com/

<sup>&</sup>lt;sup>5</sup> http://www.adaptivecomputing.com/products/maui/

changes and classified as a multi-mode dataflow model. The proposed technique minimizes the number of required processors for multiprocessor scheduling by considering task migration between modes. The focus is on minimization of required resources, but not the parameterization of resources, such as frequency scaling.

### 2.6.3. Optimization techniques for scheduling

The basic structure of the scheduling technique for *TT* communication in *NoCs* is built by formulating an *MILP* problem, as in [90], and extended to *MIQP* in this work. It consists of constants, decision variables, constraints, and an objective function, which are modeled by a set of *MIQP*-compatible equations. The *MILP* and *MIQP* problems are solved using the *IBM* optimizer.

Tariq et al. [46] investigated the problem of scheduling and energy-aware mapping on a heterogeneous *NoC* base.

Anup Das et al. [104] propose an *ILP* to reduce communication energy, fault-tolerant migration overhead, and tasks remapping.

Ishak et al. [105] worked on *nonlinear programming (NLP)* for computing and identifying the optimal frequencies for heterogeneous *NoC*-based *MPSoCs* for all tasks and communication links for an *ILP*- based algorithm. Their objective is to assign an optimal frequency for each task and each message which the total energy consumption of all the tasks and messages is minimized.

## 2.6.3.1. Quadratic Optimization

In [106], quadratic optimization (QP) is described as an essential mathematical area of NLP. It is used in most problems, including those in planning, scheduling, economics, engineering, and routing.

#### 2.6.3.2. Mixed integer quadratic programming (MIQP)

In [107], *MIQP* is used to solve scheduling problems. Here, the objective function is quadratic, concerning the integer and continuous variables, while the constraints are linear with respect to the variables of both types.

#### 2.6.3.3. Genetic algorithm (GA) and optimization techniques

Li et al. [81] worked on a *genetic algorithm* (*GA*) to achieve near-optimal voltage and frequency assignments to address the problem of energy-efficient contention-aware application mapping and scheduling in *NoCs*. Their reported results indicate that jointly utilizing dynamic voltage scaling for processors and frequency tuning *NoC* links provides excellent potential for overall energy reduction in *MPSoCs* and overall system energy consumption is significantly reduced.

Optimum solutions provide better solutions than feasible answers or other methods, such as GAs. Majd et al. [108] used GAs as they believed these to better locate a near optimal

solution than a list schedule. They report that many existing approaches do not consider communication costs when applying *GAs* to *MPSoC* scheduling problems. In contrast, we do consider the communication costs. To handle the communication delays between processors, Majd et al. used a combination of *GA* and the imperialist competitive algorithm [109], while we use *MIQP* together with the above mentioned linearization method.

At the cost of higher runtime, the *MIQP*, *MILP*, and *MIP* methods find better solutions than heuristics such as *GAs* [110].

#### 2.7. Scenario-based scheduling in event-triggered systems

Many published articles concern task scheduling with limited resources [21]. However, few works focus on scenario-based scheduling.

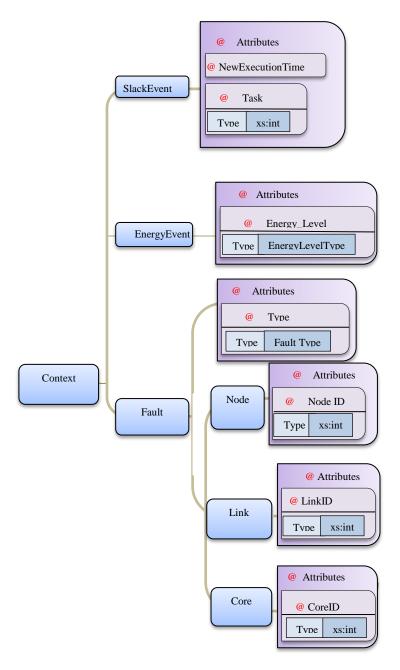

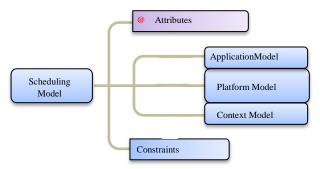

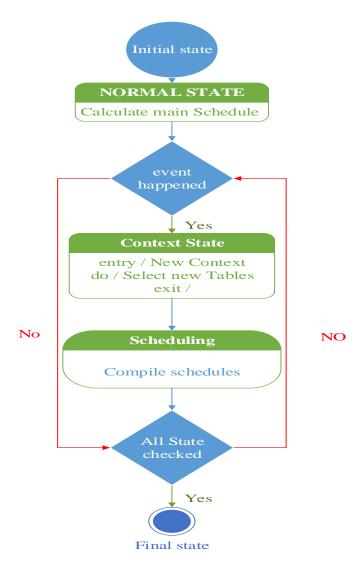

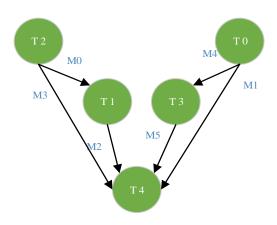

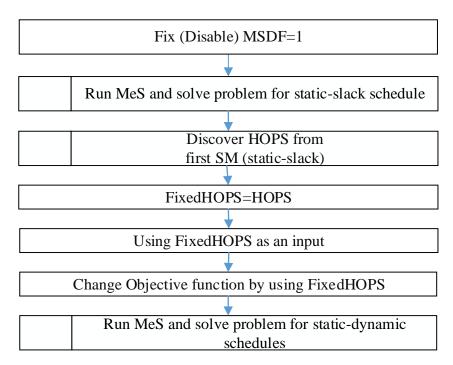

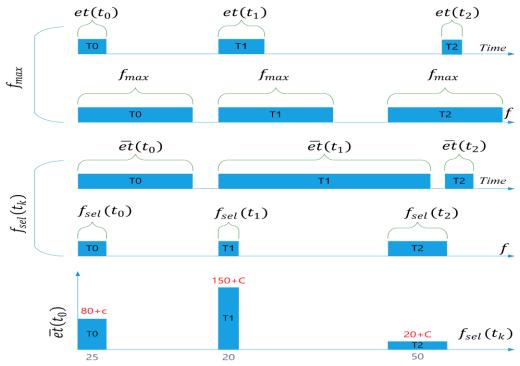

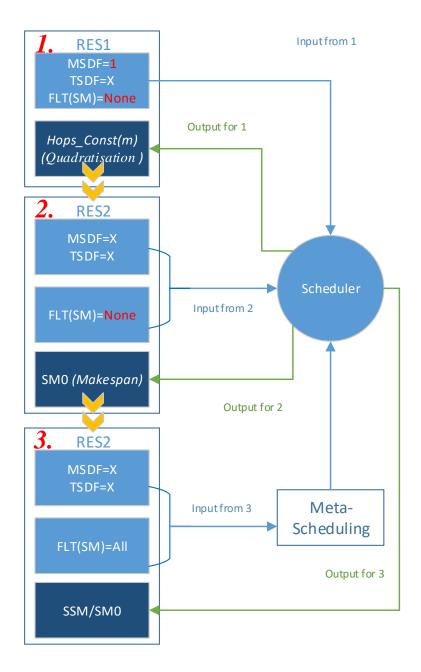

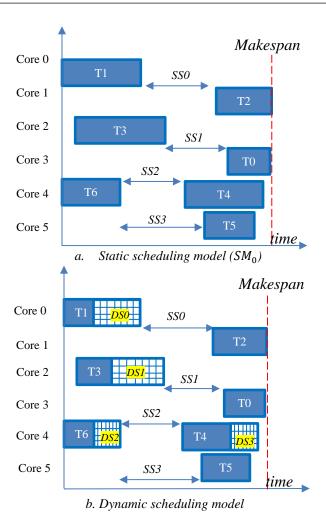

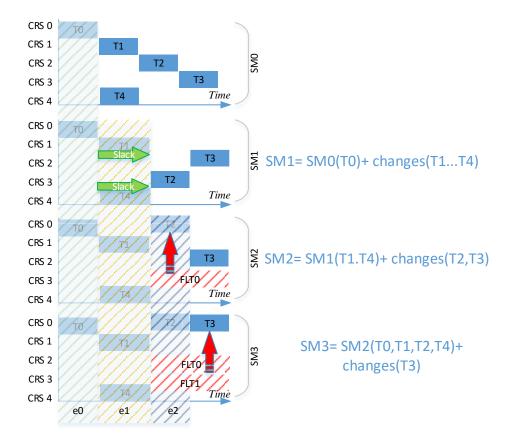

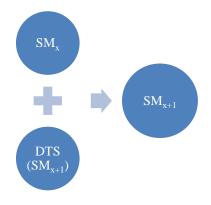

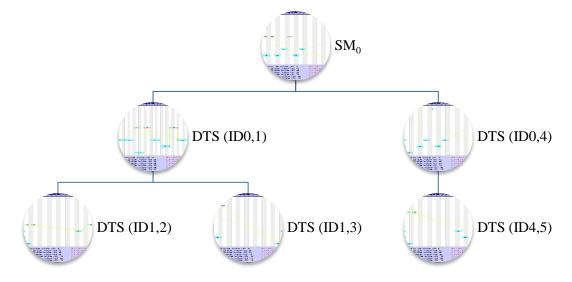

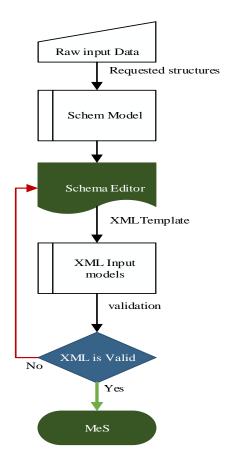

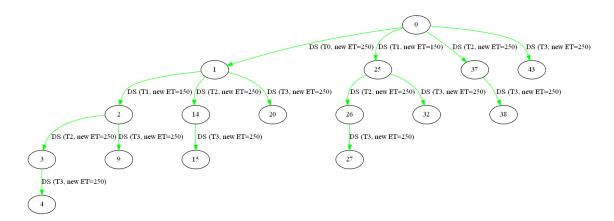

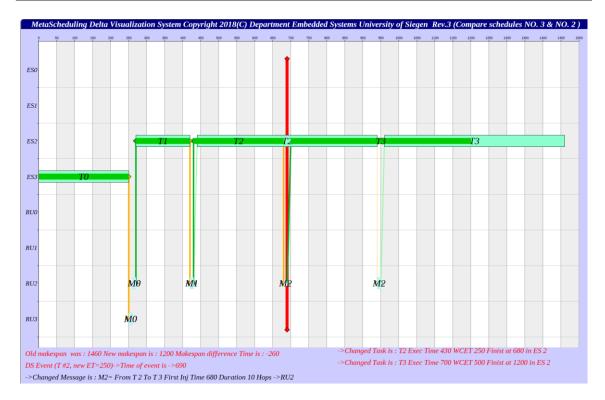

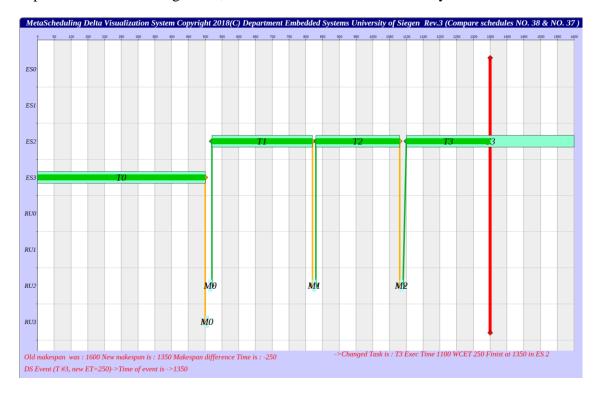

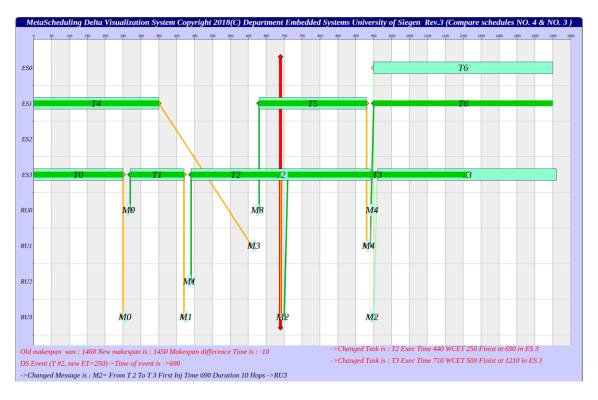

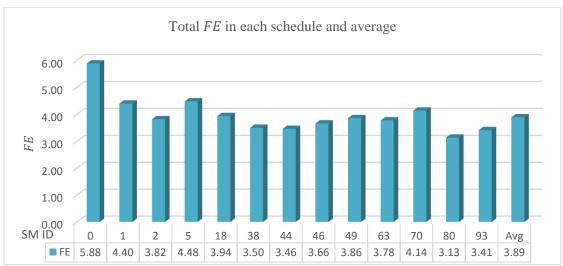

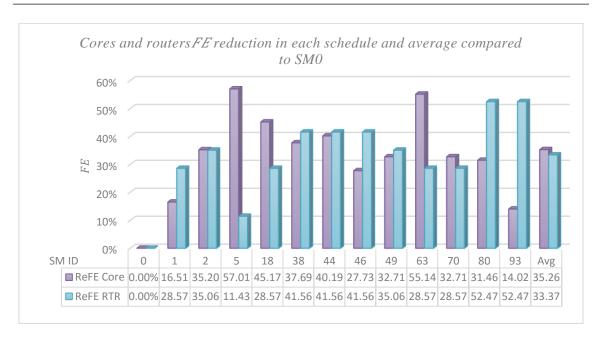

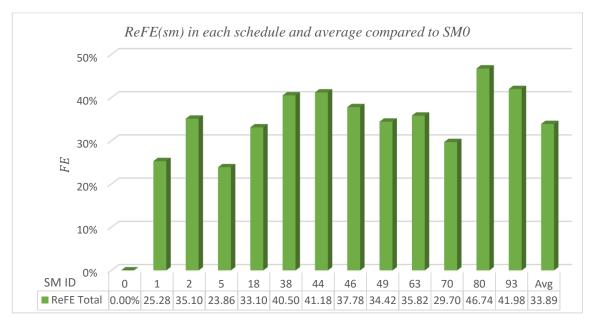

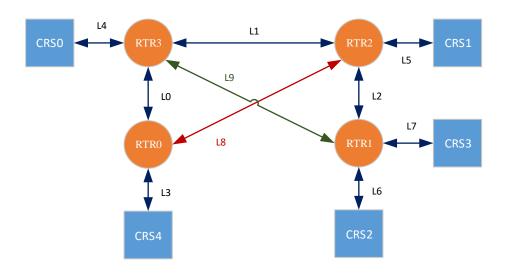

**SBMeS** is a chain solution for different scenarios of each event in the system (e.g., fault, slack), providing unique schedules and processing functions at the desired throughput. Scenario-based schedule chains are required to computationally process large volumes of constraints and variables, sometimes within very short periods, to facilitate real-time application needs.